# Descriptive Complexity: Parallelism and Circuit Complexity

### Thomas Pipilikas

#### INTER-INSTITUTIONAL GRADUATE PROGRAM "ALGORITHMS, LOGIC AND DISCRETE MATHEMATICS"

∃→ < ∃→</p>

A.L.MA.

Thomas Pipilikas

- Motivation

- Random Access Machine

- CRAM[t(n)] = IND[t(n)] = FO[t(n)]

- 2 Circuit Complexity

- Basic Definitions

- Addition in N

- Basic Theorems

### 1 Parallelism

#### Motivation

- Random Access Machine

- CRAM[t(n)] = IND[t(n)] = FO[t(n)]

### 2 Circuit Complexity

- Basic Definitions

- Addition in  $\mathbb{N}$

- Basic Theorems

A.L.MA.

Thomas Pipilikas Parallelism and Circuit Complexity

- The real world is inherently parallel

- Descriptive complexity is inherently parallel in nature.

- Quantification is a parallel operation.

(日) (四) (문) (문)

- The real world is inherently parallel

- Descriptive complexity is inherently parallel in nature.

- Quantification is a parallel operation.

- Some problems are very easy to parallelize.

- We have increased the ability to produce small, fast, inexpensive processors.

- A proccessors speed is bounded.

- Memory requirements

Image: A math a math

Motivation

### A Motivation example

#### Find all prime numbers in the interval [1, n]

#### Algorithm Sieve of Eratosthenes

Thomas Pipilikas Parallelism and Circuit Complexity

A.L.MA.

Motivation

AI MA

(日) (四) (문) (문)

### A Motivation example

#### Find all prime numbers in the interval [1, n]

### Algorithm Sieve of Eratosthenes

Start with the list of numbers 1, 2, ..., *n* represented as a "mark" bit-vector initialized to 1000...00.

Thomas Pipilikas Parallelism and Circuit Complexity

## A Motivation example

#### Find all prime numbers in the interval [1, n]

### Algorithm Sieve of Eratosthenes

Start with the list of numbers 1, 2, ..., *n* represented as a "mark" bit-vector initialized to 1000...00.

In each step, the next unmarked number m (associated with a 0 in element m of the mark bit-vector) is a prime.

## A Motivation example

#### Find all prime numbers in the interval [1, n]

### Algorithm Sieve of Eratosthenes

Start with the list of numbers 1, 2, ..., n represented as a "mark" bit-vector initialized to 1000...00.

In each step, the next unmarked number m (associated with a 0 in element m of the mark bit-vector) is a prime.

Find this element m and mark all multiples of m beginning with  $m^2$ .

## A Motivation example

#### Find all prime numbers in the interval [1, n]

### Algorithm Sieve of Eratosthenes

Start with the list of numbers 1, 2, ..., n represented as a "mark" bit-vector initialized to 1000...00.

In each step, the next unmarked number m (associated with a 0 in element m of the mark bit-vector) is a prime.

Find this element m and mark all multiples of m beginning with  $m^2$ . When  $m^2 > n$ , the computation stops and all unmarked elements are prime numbers.

AI MA

A.L.MA.

< ロ > < 回 > < 回 > < 回 > < 回 >

### A Motivation example

| 2<br>2                             |           | 4 | 5         | 6 | 7        | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 | 16 | 17         | 18 | 19 | 20 | 21 | 22 | 23 | 24 | 25 | 26 | 27 | 28 | 29 | 30 |

|------------------------------------|-----------|---|-----------|---|----------|---|---|----|----|----|----|----|----|----|------------|----|----|----|----|----|----|----|----|----|----|----|----|----|

|                                    | 3<br>17=3 |   | 5         |   | 7        |   | 9 |    | 11 |    | 13 |    | 15 |    | 17         |    | 19 |    | 21 |    | 23 |    | 25 |    | 27 |    | 29 |    |

| 2                                  | 3         |   | 5<br>//=5 |   | 7        |   |   |    | 11 |    | 13 |    |    |    | 17         |    | 19 |    |    |    | 23 |    | 25 |    |    |    | 29 |    |

| 2                                  | 3         |   | 5         |   | 7<br>m=7 |   |   |    | 11 |    | 13 |    |    |    | 1 <b>7</b> |    | 19 |    |    |    | 23 |    |    |    |    |    | 29 |    |

| Sieve of Eratosthenes for $n = 30$ |           |   |           |   |          |   |   |    |    |    |    |    |    |    |            |    |    |    |    |    |    |    |    |    |    |    |    |    |

### A Motivation example

A Single-proccessor for the algorithm

Thomas Pipilikas Parallelism and Circuit Complexity

### A Motivation example

#### A Single-proccessor for the algorithm

(日) (四) (문) (문)

A.L.MA.

(日) (同) (日) (日)

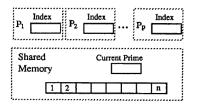

### A Motivation example

#### A Single-proccessor for the algorithm

Current Prime contains the latest prime number found (initialized to 2).

Thomas Pipilikas Parallelism and Circuit Complexity

### A Motivation example

### A Single-proccessor for the algorithm

- Current Prime contains the latest prime number found (initialized to 2).

- Index is initialized to the square of Current Prime. Then incriments by Current Prime in order to mark all of its multiples.

### A Motivation example

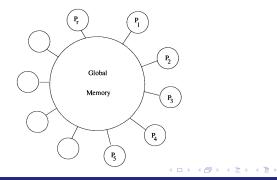

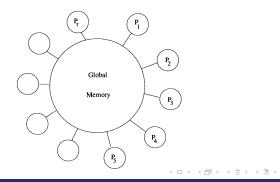

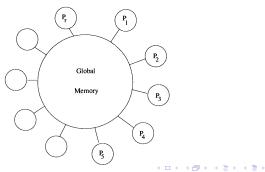

A Parallel p-proccessors machine for the algorithm

▲ロト ▲御 ト ▲臣 ト ▲臣 ト → 臣 → のへの

Thomas Pipilikas Parallelism and Circuit Complexity

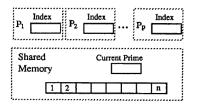

### A Motivation example

A Parallel p-proccessors machine for the algorithm

Thomas Pipilikas Parallelism and Circuit Complexity A.L.MA.

(日) (四) (문) (문)

### A Motivation example

A Parallel p-proccessors machine for the algorithm

Shared Memory contains Curent Prime and the list of numbers.

### A Motivation example

A Parallel p-proccessors machine for the algorithm

- Shared Memory contains Curent Prime and the list of numbers.

- Each *Proccessor* refers to the shared memory:

AI MA

(日) (同) (日) (日)

### A Motivation example

A Parallel p-proccessors machine for the algorithm

- Shared Memory contains Curent Prime and the list of numbers.

- Each *Proccessor* refers to the shared memory:

- Updates Current Prime

AI MA

### A Motivation example

A Parallel p-proccessors machine for the algorithm

- Shared Memory contains Curent Prime and the list of numbers.

- Each *Proccessor* refers to the shared memory:

- Updates Current Prime

- Uses its private index to step through the list and mark the multiples of the prime that updated.

Thomas Pipilikas

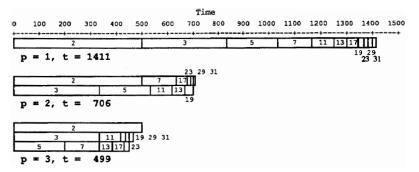

### A Motivation example

Implementation of the algorithm for  $p \in [3]$  processors and n = 1000

A.L.MA.

### A Motivation example

Implementation of the algorithm for  $p \in [3]$  processors and n = 1000

Note that by using more than three proccessors would not reduce the computation time. (Why?)

### 1 Parallelism

Motivation

#### Random Access Machine

• CRAM[t(n)] = IND[t(n)] = FO[t(n)]

### 2 Circuit Complexity

- Basic Definitions

- Addition in  $\mathbb{N}$

- Basic Theorems

A.L.MA.

Thomas Pipilikas Parallelism and Circuit Complexity Random Access Machine

A.L.MA.

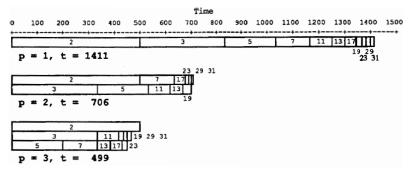

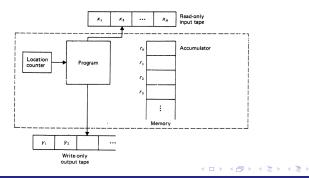

A *random access machine* (RAM) is one-accumulator computer that consists:

Thomas Pipilikas

A *random access machine* (RAM) is one-accumulator computer that consists:

A read-only input tape

Thomas Pipilikas

A *random access machine* (RAM) is one-accumulator computer that consists:

- A read-only input tape

- An infinite wright-only output tape

Thomas Pipilikas

A *random access machine* (RAM) is one-accumulator computer that consists:

- A read-only input tape

- An infinite wright-only output tape

- A program, which contains a sequence of instrutions

Thomas Pipilikas

A *random access machine* (RAM) is one-accumulator computer that consists:

- A read-only input tape

- An infinite wright-only output tape

- A program, which contains a sequence of instrutions

- A memory, which contains a sequence of registers

Thomas Pipilikas

Random Access Machine

#### Read-only input tape:

A.L.MA.

Thomas Pipilikas Parallelism and Circuit Complexity

Is a sequence of squares, each of which holds an integer (possibly negative).

#### Read-only input tape:

- Is a sequence of squares, each of which holds an integer (possibly negative).

- Whenever a symbol is read from the input tape, the tape head moves one square to the right.

- Is a sequence of squares, each of which holds an integer (possibly negative).

- Whenever a symbol is read from the input tape, the tape head moves one square to the right.

### Wright-only output tape:

- Is a sequence of squares, each of which holds an integer (possibly negative).

- Whenever a symbol is read from the input tape, the tape head moves one square to the right.

### Wright-only output tape:

Is a sequence of squares, each of which is initially blank.

- Is a sequence of squares, each of which holds an integer (possibly negative).

- Whenever a symbol is read from the input tape, the tape head moves one square to the right.

#### Wright-only output tape:

- Is a sequence of squares, each of which is initially blank.

- When a write instruction is executed, an integer is printed in the square of the output tape that is currently under the output tape head and the tape head is moved one square to the right.

- Is a sequence of squares, each of which holds an integer (possibly negative).

- Whenever a symbol is read from the input tape, the tape head moves one square to the right.

#### Wright-only output tape:

- Is a sequence of squares, each of which is initially blank.

- When a write instruction is executed, an integer is printed in the square of the output tape that is currently under the output tape head and the tape head is moved one square to the right.

- Once an output symbol has been written. it cannot be changed.

Parallelism

Random Access Machine

Memory:

A.L.MA.

### Memory:

■ Consists of a sequence of registers, *R*<sub>0</sub>, *R*<sub>1</sub>, ..., *R<sub>i</sub>*, ... (we place no upper bound on the number of registers that can be used).

A.L.MA.

#### Random Access Machine

### Memory:

- Consists of a sequence of registers, R<sub>0</sub>, R<sub>1</sub>, ..., R<sub>i</sub>, ... (we place no upper bound on the number of registers that can be used).

- We have random access to each register (indirect addresing).

- Consists of a sequence of registers, R<sub>0</sub>, R<sub>1</sub>, ..., R<sub>i</sub>, ... (we place no upper bound on the number of registers that can be used).

- We have random access to each register (indirect addresing).

- Each register is capable of holding an integer of arbitrary size.

- Consists of a sequence of registers, R<sub>0</sub>, R<sub>1</sub>, ..., R<sub>i</sub>, ... (we place no upper bound on the number of registers that can be used).

- We have random access to each register (indirect addresing).

- Each register is capable of holding an integer of arbitrary size.

- Register R<sub>0</sub> is called *accumulator* and all computation takes place in it.

- Consists of a sequence of registers, R<sub>0</sub>, R<sub>1</sub>, ..., R<sub>i</sub>, ... (we place no upper bound on the number of registers that can be used).

- We have random access to each register (indirect addresing).

- Each register is capable of holding an integer of arbitrary size.

- Register R<sub>0</sub> is called *accumulator* and all computation takes place in it.

Program:

- Consists of a sequence of registers, R<sub>0</sub>, R<sub>1</sub>, ..., R<sub>i</sub>, ... (we place no upper bound on the number of registers that can be used).

- We have random access to each register (indirect addresing).

- Each register is capable of holding an integer of arbitrary size.

- Register R<sub>0</sub> is called *accumulator* and all computation takes place in it.

### Program:

■ Is a sequence of labeled instructions.

- Consists of a sequence of registers, R<sub>0</sub>, R<sub>1</sub>, ..., R<sub>i</sub>, ... (we place no upper bound on the number of registers that can be used).

- We have random access to each register (indirect addresing).

- Each register is capable of holding an integer of arbitrary size.

- Register R<sub>0</sub> is called *accumulator* and all computation takes place in it.

Program:

- Is a sequence of labeled instructions.

- Does not modify itself.

Parallelism

Random Access Machine

Instructions:

(日) (四) (三) (三) (三) (0) (0)

arithmetic, input-output, indirect addressing, branching instructions e.t.c.

(日) (四) (문) (문)

- arithmetic, input-output, indirect addressing, branching instructions e.t.c.

- Each instruction consists of two parts:

- arithmetic, input-output, indirect addressing, branching instructions e.t.c.

- Each instruction consists of two parts:

- The operation code

- arithmetic, input-output, indirect addressing, branching instructions e.t.c.

- Each instruction consists of two parts:

- The operation code

- The address:

- arithmetic, input-output, indirect addressing, branching instructions e.t.c.

- Each instruction consists of two parts:

- The operation code

- The address: operand / label

- arithmetic, input-output, indirect addressing, branching instructions e.t.c.

- Each instruction consists of two parts:

- The operation code

- The address: operand / label

| Operation code | Address |

|----------------|---------|

| 1. LOAD        | operand |

| 2. STORE       | operand |

| 3. ADD         | operand |

| 4. SUB         | operand |

| 5. MULT        | operand |

| 6. DIV         | operand |

| 7. READ        | operand |

| 8. WRITE       | operand |

| 9. JUMP        | label   |

| 10. JGTZ       | label   |

| 11. JZERO      | label   |

| 12. HALT       |         |

Example of basic instructions

# We can define the meaning of a program P at each step with the help of two quantities:

▲□▶ ▲□▶ ▲ 三▶ ▲ 三▶ → 三 → つへで

A.L.MA.

We can define the meaning of a program  ${\cal P}$  at each step with the help of two quantities:

• The memory map  $c : \mathbb{N} \to \mathbb{Z}$ , where c(i) is the contents of the register  $R_i$ .

・ロト ・同ト ・ヨト ・ヨト

We can define the meaning of a program P at each step with the help of two quantities:

• The memory map  $c : \mathbb{N} \to \mathbb{Z}$ , where c(i) is the contents of the register  $R_i$ .

Initially,  $\forall i \in \mathbb{N}$  c(i) = 0.

Circuit Complexity

We can define the meaning of a program P at each step with the help of two quantities:

- The memory map  $c : \mathbb{N} \to \mathbb{Z}$ , where c(i) is the contents of the register  $R_i$ . Initially,  $\forall i \in \mathbb{N}$  c(i) = 0.

- The *location counter*, which determines the next instruction to execute.

・ロト ・同ト ・ヨト ・ヨト

We can define the meaning of a program P at each step with the help of two quantities:

- The memory map  $c : \mathbb{N} \to \mathbb{Z}$ , where c(i) is the contents of the register  $R_i$ . Initially,  $\forall i \in \mathbb{N}$  c(i) = 0.

- The *location counter*, which determines the next instruction to execute.

Initially, the location counter is set to the first instruction in P.

・ロト ・同ト ・ヨト ・ヨト

We can define the meaning of a program P at each step with the help of two quantities:

- The memory map  $c : \mathbb{N} \to \mathbb{Z}$ , where c(i) is the contents of the register  $R_i$ . Initially,  $\forall i \in \mathbb{N}$  c(i) = 0.

- The *location counter*, which determines the next instruction to execute.

Initially, the location counter is set to the first instruction in P.

After execution of the *k*th instruction in *P*, the location counter is automatically set to k + 1 (i.e. the next instruction), unless the *k*th instruction is **JUMP**, **HALT**, **JGTZ**. or **JZERO**.

・ロト ・同ト ・ヨト ・ヨト

Parallelism

Random Access Machine

Circuit Complexity

▲□ > ▲□ > ▲目 > ▲目 > ▲目 > ④ < ⊙

A.L.MA.

Parallelism

Random Access Machine

### **Operand:**

$$1 = i$$

: The integer *i* itself.

### Operand:

- $\mathbf{1} = i$ : The integer *i* itself.

- 2 *i* : The contents of register  $R_i$ , where  $i \in \mathbb{N}$

<ロ> <回> <回> <回> <回> <回> <回> <回> <回> <の<○</p>

A.L.MA.

## Operand:

- 1 = i: The integer *i* itself.

- 2 i : The contents of register  $R_i$ , where  $i \in \mathbb{N}$

- 3 \**i* : The contents of register  $R_j$ , where *j* is the content of register  $R_i$  ( $i \in \mathbb{N}$ ) (*indirect addressing*). If j < 0 the machine halts.

### Operand:

- 1 = i: The integer *i* itself.

- 2 i : The contents of register  $R_i$ , where  $i \in \mathbb{N}$

- 3 \**i* : The contents of register  $R_j$ , where *j* is the content of register  $R_i$  ( $i \in \mathbb{N}$ ) (*indirect addressing*). If j < 0 the machine halts.

To specify the meaning of an instruction we define v(a), the *the* value of operand a, as follows:

### Operand:

- 1 = i: The integer *i* itself.

- 2 i : The contents of register  $R_i$ , where  $i \in \mathbb{N}$

- 3 \**i* : The contents of register  $R_j$ , where *j* is the content of register  $R_i$  ( $i \in \mathbb{N}$ ) (*indirect addressing*). If j < 0 the machine halts.

To specify the meaning of an instruction we define v(a), the *the* value of operand a, as follows:

$$v(=i)=i$$

### Operand:

- 1 = i: The integer *i* itself.

- 2 i : The contents of register  $R_i$ , where  $i \in \mathbb{N}$

- 3 \**i* : The contents of register  $R_j$ , where *j* is the content of register  $R_i$  ( $i \in \mathbb{N}$ ) (*indirect addressing*). If j < 0 the machine halts.

To specify the meaning of an instruction we define v(a), the *the* value of operand a, as follows:

$$v(=i)=i$$

$$v\left(i\right)=c\left(i\right)$$

Thomas Pipilikas Parallelism and Circuit Complexity

A I MA

### Random Access Machine

### Operand:

- 1 = i: The integer *i* itself.

- 2 i : The contents of register  $R_i$ , where  $i \in \mathbb{N}$

- 3 \**i* : The contents of register  $R_j$ , where *j* is the content of register  $R_i$  ( $i \in \mathbb{N}$ ) (*indirect addressing*). If j < 0 the machine halts.

To specify the meaning of an instruction we define v(a), the *the value of operand a*, as follows:

$$v (= i) = i$$

$v (i) = c (i)$

$v (*i) = c (c (i))$

イロト イポト イヨト イヨト

Thomas Pipilikas

Parallelism and Circuit Complexity

#### Parallelism

Random Access Machine

A.L.MA.

| Instruction       | Meaning                                                          |  |  |

|-------------------|------------------------------------------------------------------|--|--|

| 1. LOAD a         | $c(0) \leftarrow v(a)$                                           |  |  |

| 2. STORE i        | $c(i) \leftarrow c(0)$                                           |  |  |

| STORE *i          | $c(c(i)) \leftarrow c(0)$                                        |  |  |

| 3. ADD a          | $c(0) \leftarrow c(0) + v(a)$                                    |  |  |

| 4. SUB a          | $c(0) \leftarrow c(0) - v(a)$                                    |  |  |

| 5. MULT a         | $c(0) \leftarrow c(0) \times v(a)$                               |  |  |

| 6. DIV a          | $c(0) \leftarrow \lfloor c(0)/v(a) \rfloor^{\dagger}$            |  |  |

| 7. READ <i>i</i>  | $c(i) \leftarrow \text{current input symbol.}$                   |  |  |

| READ *i           | $c(c(i)) \leftarrow$ current input symbol. The input tape head   |  |  |

|                   | moves one square right in either case.                           |  |  |

| 8. WRITE a        | v(a) is printed on the square of the output tape currently       |  |  |

|                   | under the output tape head. Then the tape head is moved          |  |  |

|                   | one square right.                                                |  |  |

| 9. JUMP <i>b</i>  | The location counter is set to the instruction labeled b.        |  |  |

| 10. JGTZ <i>b</i> | The location counter is set to the instruction labeled $b$ if    |  |  |

|                   | c(0) > 0; otherwise, the location counter is set to the          |  |  |

|                   | next instruction.                                                |  |  |

| 11. JZERO b       | The location counter is set to the instruction labeled $b$ if    |  |  |

|                   | $\dot{c}(0) = 0$ ; otherwise, the location counter is set to the |  |  |

|                   | next instruction.                                                |  |  |

| 12. HALT          | Execution ceases.                                                |  |  |

### The meaning of basic instructions

<ロ> <四> <四> <三</p>

Thomas Pipilikas

Parallelism and Circuit Complexity

Random Access Machine

# What does a RAM do?

- A RAM computes functions:

- A RAM can compute exactly the partial recursive functions.

Thomas Pipilikas Parallelism and Circuit Complexity

< ロ > < 回 > < 回 > < 回 > < 回 >

Random Access Machine

# What does a RAM do?

- A RAM computes functions:

- A RAM can compute exactly the partial recursive functions.

- A RAM accepts languages:

- A RAM accepts exactly the recursively enumerable languages.

イロト イボト イヨト イヨ

Random Access Machine

# What does a RAM do?

- A RAM computes functions:

- A RAM can compute exactly the partial recursive functions.

- A RAM accepts languages:

- A RAM accepts exactly the recursively enumerable languages.

Image: A mathematical states and a mathem

∃ >

Thus a RAM is a reasonable model of a computer.

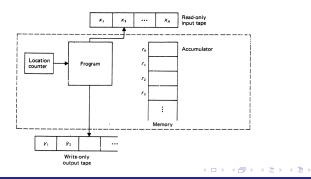

Random Access Machine

### **Example** A RAM program computing the function $f : \mathbb{Z} \to \mathbb{Z}$

$$f(n) = \begin{cases} n^n & , n \in \mathbb{N}_{>0} \\ 0 & , \text{ otherwise} \end{cases}$$

### **Example** A RAM program computing the function $f : \mathbb{Z} \to \mathbb{Z}$

#### Parallelism

#### Random Access Machine

### Solution

|                                                         | RAM   | program                                | Corresponding<br>Pidgin ALGOL statements |

|---------------------------------------------------------|-------|----------------------------------------|------------------------------------------|

|                                                         | READ  | 1                                      | read r1                                  |

|                                                         | LOAD  | 1 )                                    |                                          |

|                                                         | JGTZ  | pos                                    | if $r1 \le 0$ then write 0               |

|                                                         | WRITE | =0 )                                   |                                          |

|                                                         | JUMP  | endif                                  |                                          |

| LOAD<br>SUB                                             | LOAD  | 1 )                                    | $r^2 \leftarrow r^1$                     |

|                                                         | STORE | 2 ∫                                    | /_ \//                                   |

|                                                         | LOAD  | 1 )                                    |                                          |

|                                                         | SUB   | =1 }                                   | $r3 \leftarrow r1 - 1$                   |

|                                                         | STORE | 3 J                                    |                                          |

| JGT                                                     | LOAD  | 3                                      |                                          |

|                                                         | JGTZ  | continue }                             | while $r_3 > 0$ do                       |

|                                                         | JUMP  | endwhile)                              |                                          |

| MUL <sup>-</sup><br>STOR<br>LOAE<br>SUB<br>STOR<br>JUMP | LOAD  | 2                                      |                                          |

|                                                         | MULT  | 1                                      | $r_2 \leftarrow r_2 * r_1$               |

|                                                         | STORE | $\begin{bmatrix} 2 \\ 3 \end{bmatrix}$ |                                          |

|                                                         | LOAD  |                                        |                                          |

|                                                         |       | =1                                     | $r3 \leftarrow r3 - 1$                   |

|                                                         | STORE | 3 )                                    |                                          |

|                                                         |       | while                                  |                                          |

| endwhile:                                               | WRITE | 2                                      | write r2                                 |

| endif:                                                  | HALT  |                                        |                                          |

Thomas Pipilikas

Parallelism and Circuit Complexity

مەرە A.L.MA.

### 1 Parallelism

- Motivation

- Random Access Machine

- CRAM[t(n)] = IND[t(n)] = FO[t(n)]

### 2 Circuit Complexity

- Basic Definitions

- Addition in  $\mathbb{N}$

- Basic Theorems

< ロ > < 回 > < 回 > < 回 > < 回 >

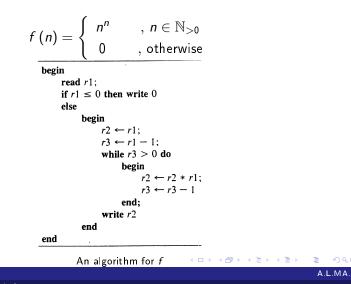

# A *parallel random-access machine* (PRAM) is a shared-memory abstract machine.

Thomas Pipilikas Parallelism and Circuit Complexity A.L.MA.

A *parallel random-access machine* (PRAM) is a shared-memory abstract machine.

■ Is the parallel-computing analogy to the RAM.

A.L.MA

A *parallel random-access machine* (PRAM) is a shared-memory abstract machine.

- Is the parallel-computing analogy to the RAM.

- It consists of a sequence of RAM's (P<sub>i</sub>)<sub>[r]</sub>, without input and output tape (each RAM uses the Global Memory).

A.L.MA.

A *parallel random-access machine* (PRAM) is a shared-memory abstract machine.

- Is the parallel-computing analogy to the RAM.

- It consists of a sequence of RAM's (P<sub>i</sub>)<sub>[r]</sub>, without input and output tape (each RAM uses the Global Memory).

- It is *synchronous* (the processors (i.e. RAM's) work in lock step).

A I MA

(日) (同) (日) (日)

Categorization accordinng to read/write conflicts.

- Exclusive read exclusive write (EREW): every memory cell can be read or written to by only one processor at a time

- 2 Concurrent read exclusive write (*CREW*): multiple processors can read a memory cell but only one can write at a time

- 3 Concurrent read concurrent write (*CRCW*): multiple processors can read and write.

Categorization accordinng to read/write conflicts.

- Exclusive read exclusive write (EREW): every memory cell can be read or written to by only one processor at a time

- 2 Concurrent read exclusive write (*CREW*): multiple processors can read a memory cell but only one can write at a time

- 3 Concurrent read concurrent write (*CRCW*): multiple processors can read and write.

Categorization of CRCW PRAM's

- **1** *Common*: all processors write the same value; otherwise is illegal

- 2 Arbitrary: only one arbitrary attempt is successful, others retire

- <u>3</u> *Priority*: processor rank indicates who gets to write

# Definition of CRAM

**CRAM** is a special type of Priority CRCW-PRAM. Each RAM has a finite set of registers, including the following:

- Processor: containing the number between 1 and p(n) of the RAM

- Address: containing an address of global memory

- Contents: containing a word to be written or read from global memory

- ProgramCounter: containing the line number of the instruction to be executed next.

RAMs are identical except the Processor number.

(日) (同) (日) (日)

A.L.MA.

(日) (四) (문) (문)

# Definition of CRAM

The instructions of a CRAM consist of the following:

READ: Read the word of Global Memory specified by Address into Contents.

# Definition of CRAM

The instructions of a CRAM consist of the following:

- READ: Read the word of Global Memory specified by Address into Contents.

- WRITE: Write the *Contents* register into the Global Memory location specified by *Address*.

(日) (同) (日) (日)

# Definition of CRAM

The instructions of a CRAM consist of the following:

- READ: Read the word of Global Memory specified by Address into Contents.

- WRITE: Write the *Contents* register into the Global Memory location specified by *Address*.

- OP  $R_a R_b$ : Perform OP on  $R_a$  and  $R_b$  and leave the result in  $R_b$ . Here OP may be Add, Subtract, or, Shift.

$\exists$  Shift(x, y) causes the word x to be shifted y bits to the right.

(日) (四) (문) (문)

# Definition of CRAM

The instructions of a CRAM consist of the following:

- READ: Read the word of Global Memory specified by Address into Contents.

- WRITE: Write the *Contents* register into the Global Memory location specified by *Address*.

- OP  $R_a R_b$ : Perform OP on  $R_a$  and  $R_b$  and leave the result in  $R_b$ . Here OP may be Add, Subtract, or, Shift.

• MOVE  $R_a R_b$ : Move  $R_a$  to  $R_b$

(日) (同) (日) (日)

# Definition of CRAM

The instructions of a CRAM consist of the following:

- READ: Read the word of Global Memory specified by Address into Contents.

- WRITE: Write the *Contents* register into the Global Memory location specified by *Address*.

- OP  $R_a R_b$ : Perform OP on  $R_a$  and  $R_b$  and leave the result in  $R_b$ . Here OP may be Add, Subtract, or, Shift.

- MOVE  $R_a R_b$ : Move  $R_a$  to  $R_b$

- **BLT** *R L*: Branch to line (adress) *L* of the Program, if the contents of *R* is less than zero.

(日) (同) (日) (日)

AI MA

# Definition of CRAM

The instructions of a CRAM consist of the following:

- READ: Read the word of Global Memory specified by Address into Contents.

- WRITE: Write the *Contents* register into the Global Memory location specified by *Address*.

- OP  $R_a R_b$ : Perform OP on  $R_a$  and  $R_b$  and leave the result in  $R_b$ . Here OP may be Add, Subtract, or, Shift.

- MOVE  $R_a R_b$ : Move  $R_a$  to  $R_b$

- **BLT** *R L*: Branch to line (adress) *L* of the Program, if the contents of *R* is less than zero.

J The above instructions each increment the ProgramCounter, with the exception of **BLT**.

Thomas Pipilikas

Parallelism and Circuit Complexity

A.L.MA.

< ロ > < 回 > < 回 > < 回 > < 回 >

The Shift operation for the CRAM allows each bit of Global Memory to be available to every processor in constant time.

- The Shift operation for the CRAM allows each bit of Global Memory to be available to every processor in constant time.

- We assume initially that the contents of the first |bin(A)| words of Global Memory contain one bit each of the input string bin(A).

(日) (同) (日) (日)

- The Shift operation for the CRAM allows each bit of Global Memory to be available to every processor in constant time.

- We assume initially that the contents of the first |bin(A)|words of Global Memory contain one bit each of the input string bin(A).

- We assume that a section of Global Memory is specified as the output.

# CRAM's complexity

#### Definitions

CRAM[t(n)]: The set of boolean queries computable in parallel time t(n) on a CRAM that has at most polynomially many processors.

Thomas Pipilikas Parallelism and Circuit Complexity

(日) (四) (문) (문)

Parallelism 0 = 0 = 0 0 = 0 = 0 0 = 0 = 0CRAM[t(n)] = IND[t(n)] = FO[t(n)]

# CRAM's complexity

### Definitions

CRAM[t(n)]: The set of boolean queries computable in parallel time t(n) on a CRAM that has at most polynomially many processors. CRAM-PROC[t(n), p(n)]: The set of boolean queries computable by a CRAM using at most p(n) processors and time O(t(n)). Parallelism 0 = 0 = 0 0 = 0 = 0 0 = 0 = 0 0 = 0 = 0 0 = 0 = 0 0 = 0 = 0 0 = 0 = 0 0 = 0 = 0 0 = 0 = 0 0 = 0 = 0 0 = 0 = 0 0 = 0 = 0 0 = 0 = 0 0 = 0 = 0 0 = 0 = 0 0 = 0 = 0 0 = 0 = 0 0 = 0 = 0 0 = 0 = 0 0 = 0 = 0 0 = 0 = 0 0 = 0 = 0 0 = 0 = 0 0 = 0 = 0 0 = 0 = 0 0 = 0 = 0 0 = 0 = 0 0 = 0 = 0 0 = 0 = 0 0 = 0 = 0 0 = 0 = 0 0 = 0 = 0 0 = 0 = 0 0 = 0 = 0 0 = 0 = 0 0 = 0 = 0 0 = 0 = 0 0 = 0 = 0 0 = 0 = 0 0 = 0 = 0 0 = 0 = 0 0 = 0 = 0 0 = 0 = 0 0 = 0 0 = 0 0 = 0 0 = 0 0 = 0 0 = 0 0 = 0 0 = 0 0 = 0 0 = 0 0 = 0 0 = 0 0 = 0 0 = 0 0 = 0 0 = 0 0 = 0 0 = 0 0 = 0 0 = 0 0 = 0 0 = 0 0 = 0 0 = 0 0 = 0 0 = 0 0 = 0 0 = 0 0 = 0 0 = 0 0 = 0 0 = 0 0 = 0 0 = 0 0 = 0 0 = 0 0 = 0 0 = 0 0 = 0 0 = 0 0 = 0 0 = 0 0 = 0 0 = 0 0 = 0 0 = 0 0 = 0 0 = 0 0 = 0 0 = 0 0 = 0 0 = 0 0 = 0 0 = 0 0 = 0 0 = 0 0 = 0 0 = 0 0 = 0 0 = 0 0 = 0 0 = 0 0 = 0 0 = 0 0 = 0 0 = 0 0 = 0 0 = 0 0 = 0 0 = 0 0 = 0 0 = 0 0 = 0 0 = 0 0 = 0 0 = 0 0 = 0 0 = 0 0 = 0 0 = 0 0 = 0 0 = 0 0 = 0 0 = 0 0 = 0 0 = 0 0 = 0 0 = 0 0 = 0 0 = 0 0 = 0 0 = 0 0 = 0 0 = 0 0 = 0 0 = 0 0 = 0 0 = 0 0 = 0 0 = 0 0 = 0 0 = 0 0 = 0 0 = 0 0 = 0 0 = 0 0 = 0 0 = 0 0 = 0 0 = 0 0 = 0 0 = 0 0 = 0 0 = 0 0 = 0 0 = 0 0 = 0 0 = 0 0 = 0 0 = 0 0 = 0 0 = 0 0 = 0 0 = 0 0 = 0 0 = 0 0 = 0 0 = 0 0 = 0 0 = 0 0 = 0 0 = 0 0 = 0 0 = 0 0 = 0 0 = 0 0 = 0 0 = 0 0 = 0 0 = 0 0 = 0 0 = 0 0 = 0 0 = 0 0 = 0 0 = 0 0 = 0 0 = 0 0 = 0 0 = 0 0 = 0 0 = 0 0 = 0 0 = 0 0 = 0 0 = 0 0 = 0 0 = 0 0 = 0 0 = 0 0 = 0 0 = 0 0 = 00 = 0

# CRAM's complexity

### Definitions

CRAM[t(n)]: The set of boolean queries computable in parallel time t(n) on a CRAM that has at most polynomially many processors. CRAM-PROC[t(n), p(n)]: The set of boolean queries computable by a CRAM using at most p(n) processors and time O(t(n)).

Thus,

$$CRAM[t(n)] = CRAM - PROC[t(n), n^{\mathcal{O}(1)}]$$

(日) (同) (日) (日)

### Definitions

Let  $\varphi(R, \vec{x})$  be an *R*-positive formula, where *R* is a relation symbol of arity *k*, and let  $\mathcal{A}$  be a structure of size *n*. Define the depth of  $\varphi$  in  $\mathcal{A}$ , in symbols  $|\varphi^{\mathcal{A}}|$ , to be the minimum *r* such that

$$\mathcal{A}\models\left(\varphi^{r}\left(\emptyset\right)\leftrightarrow\varphi^{r+1}\left(\emptyset\right)\right)$$

Define the depth of  $\varphi$  as a function of n equal to the maximum depth of  $\varphi$  in  $\mathcal{A}$  for any structure  $\mathcal{A}$  of size n:

$$|\varphi|(n) \doteq \max_{\|\mathcal{A}\|=n} \{|\varphi^{\mathcal{A}}|\}$$

IND[f(n)] be the sublanguage of FO(LFP) in which only fixed points of first-order formulas  $\varphi$  for which  $|\varphi|$  is  $\mathcal{O}[f(n)]$  are included.

Parallelism 0 = 0 = 0 = 0 0 = 0 = 0 = 0 0 = 0 = 0 = 0CRAM[t(n)] = IND[t(n)] = FO[t(n)]

# Iterating FO formulas

### Moschovakis' Canonical Form for Positive Formulas

#### Lemma

Let  $\varphi$  be an *R*-positive first-order formula and  $\vec{x} = (x_1, ..., x_k)$ . Then  $\varphi$  can be written in the following form,

$$\varphi(R, \overrightarrow{x}) \equiv (Q_1 z_1.M_1) \dots (Q_s z_s.M_s) (\exists x_1 \dots x_k.M_{s+1}) R(x_1, \dots, x_k)$$

where the  $M_i$ 's are quantifier-free formulas in which R does not occur.

<ロ> <四> <四> <三</p>

Let  $QB \doteq [(Q_1z_1.M_1)...(Q_sz_s.M_s)(\exists x_1...x_k.M_{s+1})]$ . Then  $\forall A$  structure and  $\forall r \in \mathbb{N}$

$$\mathcal{A} \models \left( \left( \varphi^{\mathcal{A}} \right)^r (\emptyset) \leftrightarrow ([\text{QB}]^r \text{ false }) \right)$$

<ロ> (日) (日) (日) (日) (日)

Let  $QB \doteq [(Q_1z_1.M_1)...(Q_sz_s.M_s)(\exists x_1...x_k.M_{s+1})]$ . Then  $\forall A$  structure and  $\forall r \in \mathbb{N}$

$$\mathcal{A} \models \left( \left( arphi^{\mathcal{A}}

ight)^r (\emptyset) \leftrightarrow ([\mathrm{QB}]^r \, \mathsf{false} \, \, )

ight)$$

Thus if  $t = |\varphi|(n)$  and  $\mathcal{A}$  is any structure of size n then

$\mathcal{A} \models \left( (\mathrm{LFP}\varphi) \leftrightarrow \left( [\mathrm{QB}]^t \, \mathsf{false} \, \right) \right)$

Thomas Pipilikas Parallelism and Circuit Complexity A.L.MA.

<ロ> <四> <四> <三</p>

A I MA

(日) (同) (日) (日)

### Definition

A set  $S \subseteq \text{STRUC}[\tau]$  is a member of FO[t(n)] iff there exist quantifier free formulas  $M_i$ ,  $i \in [s]$ , from  $\mathcal{L}(\tau)$ , a tuple  $\overrightarrow{c}$  of constants and a quantifier block,

$$QB = [(Q_1z_1.M_1)\dots(Q_sz_s.M_s)]$$

such that  $\forall \mathcal{A} \in \mathrm{STRUC}[ au]$ ,

$$\mathcal{A} \in \mathcal{S} \Leftrightarrow \mathcal{A} \models \left( [\mathrm{QB}]^{t(\|\mathcal{A}\|)} M_0 \right) \left( \overrightarrow{c} / \overrightarrow{x} \right)$$

Thomas Pipilikas

Parallelism and Circuit Complexity

Parallelism 0 = 0 = 0 0 = 0 = 0 0 = 0 = 0CRAM[t(n)] = IND[t(n)] = FO[t(n)]

### Example

Let's recall the alternative inductive definition of the reflexive transitive closure,  $E^*$ , of E, that we saw in the previous lecture:

$$\varphi^{*}(R, x, y) \equiv x = y \lor E(x, y) \lor \exists z (R(x, z) \land R(z, y))$$

with depth

$$|\varphi^*|(n) = \lceil \log n \rceil + 1$$

We want to find out how to wright this inductive definition in the Moschovakis' Canonical Form for Positive Formulas.

(日) (同) (日) (日)

A.L.MA.

(日) (四) (문) (문)

### Solution

First, code the base case using a dummy universal quantification:

$$\varphi^{*}(R, x, y) \equiv (\forall z. M_{1}) (\exists z) (R(x, z) \land R(z, y))$$

$$M_1 \equiv x = y \lor E(x, y)$$

AI MA

#### Solution

First, code the base case using a dummy universal quantification:

$$arphi^{*}(R, x, y) \equiv (\forall z. M_{1}) (\exists z) (R(x, z) \land R(z, y))$$

$M_{1} \equiv x = y \lor E(x, y)$

Next, use universal quantification to replace the two occurrences of R with a single one:

$$\varphi^* (R, x, y) \equiv (\forall z. M_1) (\exists z) (\forall uv. M_2) (R (u, v))$$

$$M_2 \equiv (u = x \land v = z) \lor (u = z \land v = y)$$

< ロ > < 回 > < 回 > < 回 > < 回 >

Thomas Pipilikas

Parallelism and Circuit Complexity

A.L.MA.

<ロ> <四> <四> <三</p>

### Solution

Finally, requantify x and y:

$$\varphi^* (R, x, y) \equiv (\forall z.M_1) (\exists z) (\forall uv.M_2) (\exists xy.M_3) R (x, y)$$

$$M_3 \equiv (x = u \land v = y)$$

Define the quantifier block:

$\mathrm{QB}^{*} \equiv (\forall z.M_{1}) (\exists z) (\forall uv.M_{2}) (\exists xy.M_{3})$

<□>

<□>

### Define the quantifier block:

$$QB^* \equiv (\forall z.M_1) (\exists z) (\forall uv.M_2) (\exists xy.M_3)$$

Thus  $\forall r \in \mathbb{N}$ :

$$\varphi^{*'}(\emptyset) \equiv [QB^*]^r \text{ (false)}$$

Thomas Pipilikas Parallelism and Circuit Complexity

(日) (四) (문) (문)

A.L.MA.

< ロ > < 回 > < 回 > < 回 > < 回 >

### Define the quantifier block:

$$QB^* \equiv (\forall z.M_1) (\exists z) (\forall uv.M_2) (\exists xy.M_3)$$

Thus  $\forall r \in \mathbb{N}$ :

$$\varphi^{*'}(\emptyset) \equiv [\mathrm{QB}^*]^r \,(\mathsf{false})$$

The boolean query REACH is expressible as:

$$\operatorname{REACH} \equiv \left( \operatorname{LFP}_{R_{xy}} \varphi^* \right) (s, t)$$

### Define the quantifier block:

$$QB^* \equiv (\forall z.M_1) (\exists z) (\forall uv.M_2) (\exists xy.M_3)$$

Thus  $\forall r \in \mathbb{N}$ :

$$\varphi^{*'}(\emptyset) \equiv [\mathrm{QB}^*]^r \,(\mathsf{false})$$

The boolean query  $\operatorname{REACH}$  is expressible as:

$$\operatorname{REACH} \equiv \left(\operatorname{LFP}_{R_{xy}}\varphi^{*}\right)(s,t)$$

Thus by previous example we have that

$\text{REACH} \in \text{FO}[\log n]$

Thomas Pipilikas Parallelism and Circuit Complexity

э

(ロ) (四) (三) (三)

### We are ready to prove the main Theorem of this Section.

▲口▶ ▲圖▶ ▲理▶ ▲理▶ ― 臣 … のへで

We are ready to prove the main Theorem of this Section.

#### Theorem

Let S be a boolean query. For all polynomially bounded, parallel time constructible t(n), the following are equivalent:

- S is computable by a CRAM in parallel time t(n) using polynomially many processors and registers of polynomially bounded word size.

- 2 *S* is definable as a uniform first-order induction whose depth, for structures of size *n*, is at most *t*(*n*).

- 3 There exists a first-order quantifier-block [QB], a quantifier-free formula  $M_0$  and a tuple  $\vec{c}$  of constants such that the query S for structures of size at most n is expressed as  $[QB]^{t(n)}M_0(\vec{c}/\vec{x})$ .

イロト イボト イヨト イヨト

### In symbols, the previous theorem can be stated as:

### $\operatorname{CRAM}[t(n)] = \operatorname{IND}[t(n)] = \operatorname{FO}[t(n)]$

In symbols, the previous theorem can be stated as:

$\mathrm{CRAM}[t(n)] = \mathrm{IND}[t(n)] = \mathrm{FO}[t(n)]$

In order to prove this theorem we will need 3 Lemmas.

Thomas Pipilikas Parallelism and Circuit Complexity

< ロ > < 回 > < 回 > < 回 > < 回 >

#### Lemma

For all t(n) and all classes of finite structures,

# $\operatorname{IND}\left[t\left(n\right)\right]\subseteq\operatorname{FO}\left[t\left(n\right)\right]$

Thomas Pipilikas Parallelism and Circuit Complexity

<ロ> (日) (日) (日) (日) (日)

A.L.MA.

<ロ> (日) (日) (日) (日) (日)

#### Lemma

For all t(n) and all classes of finite structures,

# $\operatorname{IND}\left[t\left(n\right)\right]\subseteq\operatorname{FO}\left[t\left(n ight) ight]$

### Proof.

Hint: Previous lemma and straight forward from definitions.

#### Lemma

For any polynomially bounded t(n) we have,

$\operatorname{CRAM}\left[t\left(n\right)\right]\subseteq\operatorname{IND}\left[t\left(n\right)\right]$

Thomas Pipilikas Parallelism and Circuit Complexity

Parallelism 0 = 0 = 0 = 0 0 = 0 = 0 = 0 0 = 0 = 0 = 0CRAM[t(n)] = IND[t(n)] = FO[t(n)]

#### Lemma

For any polynomially bounded t(n) we have,

$\operatorname{CRAM}[t(n)] \subseteq \operatorname{IND}[t(n)]$

# Proof.

**Sketching of solution:** We want to simulate the computation of a CRAM M, on input  $\mathcal{A}$ :  $||\mathcal{A}|| = n$ , by defining the contents of all the relevant registers for any processor of M by induction on the time step, through a relation VALUE $(\overline{p}, \overline{t}, \overline{x}, r, b)$ , meaning that bit  $\overline{x}$  in register r of processor p just after step t is equal to b.

CRAM[*t*(*n*)] = IND[*t*(*n*)] = FO[*t*(*n*)]

# Proof.

We need constant number of variables x<sub>1</sub>,..., x<sub>k</sub> each ranging over the *n* element universe of A, to name any bit in any register belonging to any processor at any step of the computation.

- We need constant number of variables x<sub>1</sub>,..., x<sub>k</sub> each ranging over the *n* element universe of A, to name any bit in any register belonging to any processor at any step of the computation.

- For  $\overline{t} = 0$  the memory is correctly loaded with  $bin(\mathcal{A})$ .

- We need constant number of variables x<sub>1</sub>,..., x<sub>k</sub> each ranging over the *n* element universe of A, to name any bit in any register belonging to any processor at any step of the computation.

- For  $\overline{t} = 0$  the memory is correctly loaded with  $bin(\mathcal{A})$ .

- The inductive definition of the relation  $VALUE(\bar{p}, \bar{t}, \bar{x}, r, b)$  is a disjunction depending on the value of p's ProgramCounter at time  $\bar{t} - 1$ .

- We need constant number of variables x<sub>1</sub>,..., x<sub>k</sub> each ranging over the *n* element universe of A, to name any bit in any register belonging to any processor at any step of the computation.

- For  $\overline{t} = 0$  the memory is correctly loaded with  $bin(\mathcal{A})$ .

- The inductive definition of the relation  $VALUE(\bar{p}, \bar{t}, \bar{x}, r, b)$  is a disjunction depending on the value of p's ProgramCounter at time  $\bar{t} - 1$ .

- **Addition**, **Subtraction**, **BLT** are first-order expressible.

- We need constant number of variables x<sub>1</sub>,..., x<sub>k</sub> each ranging over the *n* element universe of A, to name any bit in any register belonging to any processor at any step of the computation.

- For  $\overline{t} = 0$  the memory is correctly loaded with  $bin(\mathcal{A})$ .

- The inductive definition of the relation  $VALUE(\bar{p}, \bar{t}, \bar{x}, r, b)$  is a disjunction depending on the value of p's ProgramCounter at time  $\bar{t} - 1$ .

- **Addition**, **Subtraction**, **BLT** are first-order expressible.

- **Shift** is first-order expressible due to relation BIT.

AI MA

# Proof.

- We need constant number of variables x<sub>1</sub>,..., x<sub>k</sub> each ranging over the *n* element universe of A, to name any bit in any register belonging to any processor at any step of the computation.

- For  $\overline{t} = 0$  the memory is correctly loaded with  $bin(\mathcal{A})$ .

- The inductive definition of the relation  $VALUE(\overline{p}, \overline{t}, \overline{x}, r, b)$  is a disjunction depending on the value of p's ProgramCounter at time  $\overline{t} - 1$ .

- **Addition**, **Subtraction**, **BLT** are first-order expressible.

- **Shift** is first-order expressible due to relation BIT.

Thus we describe an inductive definition of relation VALUE, coding M's entire computation.

Thomas Pipilikas

Parallelism and Circuit Complexity

#### Lemma

For polynomially bounded and parallel time constructible t(n),

$\mathrm{FO}\left[t\left(n\right)\right]\subseteq\mathrm{CRAM}\left[t\left(n\right)\right]$

<□>

<□>

A.L.MA.

#### Lemma

For polynomially bounded and parallel time constructible t(n),

FO  $[t(n)] \subseteq CRAM [t(n)]$

### Proof.

Let the FO[t(n)] problem be determined by the following quantifier free formulas, quantifier block, and tuple of constants,

$$M_0, \ldots, M_k$$

;  $QB = (Q_1 x_1.M_1) \ldots (Q_k x_k.M_k); \overrightarrow{c}$

Our CRAM must test whether an input structure A, so that ||A|| = n satisfies the sentence,

$$\varphi_n \equiv [\text{QB}]^{t(n)} M_0 \left(\overrightarrow{c}/\overrightarrow{x}\right)$$

Thomas Pipilikas

Parallelism and Circuit Complexity

CRAM[t(n)] = IND[t(n)] = FO[t(n)]

#

### Proof.

The CRAM will: use n<sup>k</sup> processors (RAMs)

A.L.MA.

# Proof.

The CRAM will:

■ use *n<sup>k</sup>* processors (RAMs)

- Each processor will have a number  $a_1...a_k$ , where  $a_i \in \{0, ..., n-1\} \doteq n$

- Using the Shift operation it can retrieve each of the a<sub>i</sub>'s in constant time.

# Proof.

# The CRAM will:

- use *n<sup>k</sup>* processors (RAMs)

- Each processor will have a number  $a_1...a_k$ , where  $a_i \in \{0, ..., n-1\} \doteq n$

- Using the Shift operation it can retrieve each of the a<sub>i</sub>'s in constant time.

- use  $n^{k-1}$  bits of Global Memory

CRAM[t(n)] = IND[t(n)] = FO[t(n)]

# Proof.

- The CRAM will:

- use *n<sup>k</sup>* processors (RAMs)

- Each processor will have a number  $a_1...a_k$ , where  $a_i \in \{0, ..., n-1\} \doteq n$

- Using the Shift operation it can retrieve each of the a<sub>i</sub>'s in constant time.

- use  $n^{k-1}$  bits of Global Memory

- evaluate φ<sub>n</sub> from right to left, simultaneously for all values of the variables x<sub>1</sub>,...,x<sub>k</sub>.

### Proof.

We will denote for  $q \in t(n)$ ,  $i \in [k]$  and  $r = k \cdot (q+1) + 1 - i$

$\varphi^r \equiv (Q_i x_i.M_i) \dots (Q_k x_k.M_k) \, [\text{QB}]^q \, M_0$

### Proof.

We will denote for  $q \in t(n)$ ,  $i \in [k]$  and  $r = k \cdot (q+1) + 1 - i$

$$\varphi^{r} \equiv \left(Q_{i}x_{i}.M_{i}\right)...\left(Q_{k}x_{k}.M_{k}\right)\left[\text{QB}\right]^{q}M_{0}$$

That is

$$\varphi^{1} \equiv \left( Q_{k} x_{k}.M_{k} \right) M_{0}, \quad \varphi^{2} \equiv \left( Q_{k-1} x_{k-1}.M_{k-1} \right) \left( Q_{k} x_{k}.M_{k} \right) M_{0}, \dots$$

### Proof.

We will denote for  $q \in t(n)$ ,  $i \in [k]$  and  $r = k \cdot (q+1) + 1 - i$

$$\varphi^{r} \equiv \left(Q_{i}x_{i}.M_{i}\right)...\left(Q_{k}x_{k}.M_{k}\right)\left[\text{QB}\right]^{q}M_{0}$$

That is

$$\varphi^{1} \equiv (Q_{k}x_{k}.M_{k})M_{0}, \quad \varphi^{2} \equiv (Q_{k-1}x_{k-1}.M_{k-1})(Q_{k}x_{k}.M_{k})M_{0}, \dots$$

$\varphi^k \equiv [QB] M_0, \quad \varphi^{k+1} \equiv (Q_k x_k.M_k) [QB] M_0, \dots$

Thomas Pipilikas Parallelism and Circuit Complexity

### Proof.

We will denote for  $q \in t(n)$ ,  $i \in [k]$  and  $r = k \cdot (q+1) + 1 - i$

$$\varphi^{r} \equiv \left(Q_{i}x_{i}.M_{i}\right)...\left(Q_{k}x_{k}.M_{k}\right)\left[\text{QB}\right]^{q}M_{0}$$

That is

$$\varphi^{1} \equiv (Q_{k}x_{k}.M_{k})M_{0}, \quad \varphi^{2} \equiv (Q_{k-1}x_{k-1}.M_{k-1})(Q_{k}x_{k}.M_{k})M_{0}, \dots$$

$$\varphi^{k} \equiv [\text{QB}] M_{0}, \quad \varphi^{k+1} \equiv (Q_{k} x_{k}.M_{k}) [\text{QB}] M_{0}, \dots$$

$\varphi^{t(n)k} \equiv \left[ \text{QB} \right]^{t(n)} M_0$

Thomas Pipilikas

Parallelism and Circuit Complexity

### Proof.

We will denote for  $q \in t(n)$ ,  $i \in [k]$  and  $r = k \cdot (q+1) + 1 - i$

$$\varphi^{r} \equiv \left(Q_{i}x_{i}.M_{i}\right)...\left(Q_{k}x_{k}.M_{k}\right)\left[\text{QB}\right]^{q}M_{0}$$

That is

$$\varphi^{1} \equiv \left( Q_{k} x_{k}.M_{k} \right) M_{0}, \quad \varphi^{2} \equiv \left( Q_{k-1} x_{k-1}.M_{k-1} \right) \left( Q_{k} x_{k}.M_{k} \right) M_{0}, \dots$$

$$\varphi^{k} \equiv [\text{QB}] M_{0}, \quad \varphi^{k+1} \equiv (Q_{k} x_{k}.M_{k}) [\text{QB}] M_{0}, \dots$$

$$\varphi^{t(n)k} \equiv [\text{QB}]^{t(n)} M_0$$

We will denote with  $x_1...\hat{x}_i...x_k$  the k-1-tuple resulting from  $x_1...x_k$  by removing  $x_i$ .

Thomas Pipilikas

Parallelism and Circuit Complexity

We will now give a program for the CRAM which is broken into rounds each consisting of three processor steps such that: Just after round r, the contents of memory location  $a_1...\hat{a}_i...a_k$  is 1 or 0 according as whether  $\mathcal{A} \models \varphi^r(a_1, ..., a_k)$  or not (Each processor  $a_1...a_k$ , at step r + 1 sets b := 1 iff  $\mathcal{A} \models \varphi^r$ .).

We will now give a program for the CRAM which is broken into rounds each consisting of three processor steps such that: Just after round r, the contents of memory location  $a_1...\hat{a}_i...a_k$  is 1 or 0 according as whether  $\mathcal{A} \models \varphi^r(a_1, ..., a_k)$  or not (Each processor  $a_1...a_k$ , at step r + 1 sets b := 1 iff  $\mathcal{A} \models \varphi^r$ .).

Base case: At step 1, processor  $a_1 \dots a_k$  must set:

$$b = 1 \iff \mathcal{A} \models M_0(a_1, ..., a_k)$$

Thomas Pipilikas

Parallelism and Circuit Complexity

200

A I MA

CRAM[t(n)] = IND[t(n)] = FO[t(n)]

A.L.MA.

# Proof.

# Inductive step:

At round r, processor number  $a_1...a_k$  executes the following three instructions according to whether  $Q_i$  is  $\exists$  or  $Q_i$  is  $\forall$ :

# Inductive step:

At round r, processor number  $a_1...a_k$  executes the following three instructions according to whether  $Q_i$  is  $\exists$  or  $Q_i$  is  $\forall$ :  $Q_i$  is  $\exists$

1

$$b \coloneqq loc(a_1...a_{i+1}...a_k);$$

2

$$loc(a_1...\hat{a}_i...a_k) := 0;$$

3 If  $M_i(a_1,...,a_k)$  and b then  $loc(a_1...\hat{a_i}...a_k) \coloneqq 1;$

# Inductive step:

At round r, processor number  $a_1...a_k$  executes the following three instructions according to whether  $Q_i$  is  $\exists$  or  $Q_i$  is  $\forall$ :  $Q_i$  is  $\exists$

1

$$b := loc(a_1...a_{i+1}...a_k);$$

2

$$loc(a_1...\hat{a}_i...a_k) \coloneqq 0;$$

3 If  $M_i(a_1,...,a_k)$  and b then  $loc(a_1...\hat{a}_i...a_k) := 1$ ;  $Q_i$  is  $\forall$

1

$$b := loc(a_1...a_{i+1}...a_k);$$

2  $loc(a_1...\hat{a}_i...a_k) := 1;$

3 If  $M_i(a_1, ..., a_k)$  and  $\neg b$  then  $loc(a_1...\hat{a}_i...a_k) := 0;$

From the three previous lemmas we prove the requested Theorem.

A.L.MA.

# From the three previous lemmas we prove the requested Theorem.

- Motivation

- Random Access Machine

- CRAM[t(n)] = IND[t(n)] = FO[t(n)]

# 2 Circuit Complexity

- Basic Definitions

- Addition in  $\mathbb{N}$

- Basic Theorems

A.L.MA.

#### **Basic Definitions**

# Definition

A boolean circuit is a directed acyclic graph (DAG)

$$C = (V, E, G_{\wedge}, G_{\vee}, G_{\neg}, I, r)$$

where  $\tau_c \doteq \langle E^2, G^1_{\wedge}, G^1_{\vee}, G^1_{\neg}, I^1, r \rangle$  (vocabulery of circuits). An internal node w is:

- an and-gate iff  $G_{\wedge}$  holds

- an or-gate iff  $G_{\vee}$  holds

- an not-gate iff *G*, holds

- called a leaf iff it has no incoming edges and leaf w is on iff I(w) holds

Define **Circuit Value Problem** (CVP) to consist of those circuits the root gate of which evaluate to one.

A.L.MA.

(日) (同) (日) (日)

Let  $\mathcal{A} \in \operatorname{STRUC}[\tau]$  and  $||\mathcal{A}|| = n$ . A circuit  $C_n$ , with  $\hat{n}_{\tau}(n) \doteq ||\operatorname{bin}_{\tau}(\mathcal{A})||$  leaves, can take  $\mathcal{A}$  as input by placing the binary string  $\operatorname{bin}_{\tau}(\mathcal{A})$  into its leaves.

**Basic Definitions**

Let  $\mathcal{A} \in \operatorname{STRUC}[\tau]$  and  $||\mathcal{A}|| = n$ . A circuit  $C_n$ , with  $\hat{n}_{\tau}(n) \doteq ||\operatorname{bin}_{\tau}(\mathcal{A})||$  leaves, can take  $\mathcal{A}$  as input by placing the binary string  $\operatorname{bin}_{\tau}(\mathcal{A})$  into its leaves.

We write C(w) to denote the output of circuit C on input w, i.e., the value of the root node r when w is placed at the leaves and C is then evaluated.

#### **Basic Definitions**

Let  $\mathcal{A} \in \operatorname{STRUC}[\tau]$  and  $||\mathcal{A}|| = n$ . A circuit  $C_n$ , with  $\hat{n}_{\tau}(n) \doteq ||\operatorname{bin}_{\tau}(\mathcal{A})||$  leaves, can take  $\mathcal{A}$  as input by placing the binary string  $\operatorname{bin}_{\tau}(\mathcal{A})$  into its leaves.

We write C(w) to denote the output of circuit C on input w, i.e., the value of the root node r when w is placed at the leaves and C is then evaluated.

We say that circuit C accepts structure A iff  $C(bin_{\tau}(A)) = 1$ .

A.L.MA.

#### **Basic Definitions**

Let  $S \subseteq \text{STRUC}[\tau_s]$  be a boolean query on binary strings. Let  $\mathcal{C} = \{C_i\}_{\mathbb{N} \ge 1}$  an infinite sequence of circuits, where  $C_n$  is a circuit with n input bits. We say that  $\mathcal{C}$  computes S iff for all  $n \in \mathbb{N}_{\ge 1}$  and for all

We say that  $\mathcal C$  computes S iff for all  $n\in\mathbb N_{\geq 1}$  and for all  $w\in\{0,1\}^n$ ,

$w \in S \iff C_n(w) = 1$

(日) (同) (日) (日)

Parallelism and Circuit Complexity

Thomas Pipilikas

Let  $S \subseteq \text{STRUC}[\tau_s]$  be a boolean query on binary strings. Let  $\mathcal{C} = \{C_i\}_{\mathbb{N}_{\geq 1}}$  an infinite sequence of circuits, where  $C_n$  is a circuit with n input bits. We say that  $\mathcal{C}$  computes S iff for all  $n \in \mathbb{N}_{\geq 1}$  and for all  $w \in \{0, 1\}^n$ .

$w \in S \iff C_n(w) = 1$

A **threshold gate** with threshold value *i* has output one iff at least *i* of its inputs have value one.

We generalize the vocabulary of circuits to the vocabulary of threshold circuits,  $\tau_{thc} \doteq \tau_c \cup \{G_t^2\}$ , where  $G_t(g, k)$  means that g is a threshold gate with threshold value k.

・ロト ・同ト ・ヨト ・ヨト

AI MA

・ロト ・同ト ・ヨト ・ヨト

# Definition

Let C be a sequence of circuits as above. Let  $\tau \in \{\tau_c, \tau_{thc}\}$ . Let  $I : \operatorname{STRUC}[\tau_s] \to \operatorname{STRUC}[\tau]$  be a query such that for all  $n \in \mathbb{N}, I(0^n) = C_n$ . Then:

- If  $I \in FO$ , then C is a *first-order uniform* sequence of circuits.

- If  $I \in L$ , then C is a *logspace uniform*.

- If  $I \in P$ , then C is a polynomial-time uniform.

- e.t.c.

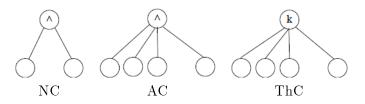

In the next frame we will define 3 families of circuit complexity classes. They vary depending on whether:

- all gates have bounded fan-in (NC)

- the "and" and "or" gates may have unbounded fan-in (AC)

• there are threshold gates (ThC)

## Parallelism

#### **Basic Definitions**

### Definition

Let t(n) be a polynomially bounded function and  $S \subseteq \text{STRUC}[\tau]$ be a boolean query. Then S is in the *(first-order uniform) circuit* complexity class NC[t(n)], AC[t(n)], ThC[t(n)], respectively iff there exists a first-order query  $I : \text{STRUC}[\tau_s] \to \text{STRUC}[\tau_{thc}]$ defining a uniform class of circuits  $C = \{C_n \mid C_n \neq I(0^n)\}$  with the following properties:

A.L.MA.

#### **Basic Definitions**

### Definition

Let t(n) be a polynomially bounded function and  $S \subseteq \text{STRUC}[\tau]$ be a boolean query. Then S is in the *(first-order uniform) circuit* complexity class NC[t(n)], AC[t(n)], ThC[t(n)], respectively iff there exists a first-order query  $I : \text{STRUC}[\tau_s] \to \text{STRUC}[\tau_{thc}]$ defining a uniform class of circuits  $C = \{C_n \mid C_n \neq I(0^n)\}$  with the following properties:

- $\ \ \, \hbox{I For all } \mathcal{A}\in \mathrm{STRUC}[\tau], \ \ \mathcal{A}\in S \iff \ \mathcal{C}_{\|\mathcal{A}\|} \ \text{accepts } \mathcal{A}.$

- **2** The depth of  $C_n$  is  $\mathcal{O}(t(n))$ .

- **3** The gates of  $C_n$  consist of binary "and" and "or" gates (NC), unbounded fan-in "and" and "or" gates (AC), and unbounded fan-in threshold gates (ThC), respectively.

### Definition

Let t(n) be a polynomially bounded function and  $S \subseteq \text{STRUC}[\tau]$ be a boolean query. Then S is in the *(first-order uniform) circuit* complexity class NC[t(n)], AC[t(n)], ThC[t(n)], respectively iff there exists a first-order query  $I : \text{STRUC}[\tau_s] \to \text{STRUC}[\tau_{thc}]$ defining a uniform class of circuits  $C = \{C_n \mid C_n \neq I(0^n)\}$  with the following properties:

- $\ \ \, \hbox{I For all } \mathcal{A}\in \mathrm{STRUC}[\tau], \ \ \mathcal{A}\in S \iff \ \mathcal{C}_{\|\mathcal{A}\|} \ \text{accepts } \mathcal{A}.$

- **2** The depth of  $C_n$  is  $\mathcal{O}(t(n))$ .

- 3 The gates of  $C_n$  consist of binary "and" and "or" gates (NC), unbounded fan-in "and" and "or" gates (AC), and unbounded fan-in threshold gates (ThC), respectively.

For  $i \in \mathbb{N}$  we denote  $\mathrm{NC}^i \doteq \mathrm{NC}[(\log n)^i]$  and similarly the  $\mathrm{AC}^i$  and  $\mathrm{ThC}^i$ . Also,  $\mathrm{NC} \doteq \bigcup \mathrm{NC}^i$ .

#### $\textbf{Addition in } \mathbb{N}$

# 1 Parallelism

- Motivation

- Random Access Machine

- CRAM[t(n)] = IND[t(n)] = FO[t(n)]

# 2 Circuit Complexity

- Basic Definitions

- Addition in N

- Basic Theorems

Thomas Pipilikas Parallelism and Circuit Complexity

Addition in  $\mathbb{N}$

## Proposition

Addition of natural numbers, represented in binary, is first-order expressible.

Thomas Pipilikas Parallelism and Circuit Complexity

#### Addition in $\mathbb N$

## Proposition

Addition of natural numbers, represented in binary, is first-order expressible.

We have already proven this Proposition using the well-known "carry-look-ahead" algorithm, through the formula  $\varphi_{add}$ , where:

- $\varphi_{carry}(x) \equiv (\exists y.y < x) [A(y) \land B(y) \land (\forall z.y < z < x) [A(z) \lor B(z)]]$ •  $a \oplus b \equiv (a \lor b) \land (\neg a \lor \neg b)$

- $\varphi_{add} \equiv A(x) \oplus B(x) \oplus \varphi_{carry}(x)$

We assumed that the columns are denoted n - 1, ..., 0 and the numbers similarly  $a = a_{n-1}...a_0$ .

・ロト ・同ト ・ヨト ・ヨト

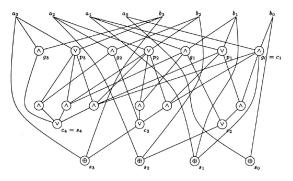

We want to express the formula  $\varphi_{\textit{add}}$  through a boolean circuit. Let:

We have:

$$c_i \doteq \varphi_{carry}(i) \equiv \bigvee_{j=0}^{i-1} \left( g_j \wedge \bigwedge_{k=j+1}^{i-1} p_k \right)$$

・ロト・四ト・ヨト・ヨト・日・ つへぐ

A.L.MA.

Thomas Pipilikas

It is easy to see that the boolean circuit bellow computes the addition for n = 4

Thomas Pipilikas Parallelism and Circuit Complexity

AI MA

It is easy to see that depth of the equivalent circuit, resulted after the raplaement of the  $\oplus$ -gates with some "and", "or" and "not" gates, is constant (why?). Thus Addition of two natural numbers is computable in  $AC^0$ . It is easy to see that depth of the equivalent circuit, resulted after the raplaement of the  $\oplus$ -gates with some "and", "or" and "not" gates, is constant (why?). Thus Addition of two natural numbers is computable in  $AC^0$ . Every input in the new circuit can have at most *n* inputs. Therefore we can simulate each "and" ("or") gates with fan-in greater than 2,

with at most log n "and" ("or") binary gates. Thus Addition of two natural numbers is computable in  $NC^1$ .

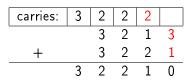

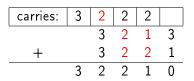

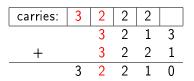

Let us calculate addition of two natural numbers using ambiguous arithmetic notation. That is a representation of natural numbers in binary, except that digits 0, 1, 2, 3 may be used. For example:

$3213 = 3 \cdot 2^3 + 2 \cdot 2^2 + 1 \cdot 2^1 + 3 \cdot 2^0 = 37 = 3221 = 3 \cdot 2^3 + 2 \cdot 2^2 + 2 \cdot 2^1 + 1 \cdot 2^0$

We observe that we can calculate the carry from column i, by looking only at columns i - 1 and i - 2.

| carries: | 3 | 2 | 2 | 3 |   |

|----------|---|---|---|---|---|

|          |   | 3 | 2 | 1 | 3 |

| +        |   | 3 | 2 | 1 | 3 |

|          | 3 | 2 | 2 | 1 | 0 |

(日) (同) (日) (日)

Let us calculate addition of two natural numbers using ambiguous arithmetic notation. That is a representation of natural numbers in binary, except that digits 0, 1, 2, 3 may be used. For example:

$3213 = 3 \cdot 2^3 + 2 \cdot 2^2 + 1 \cdot 2^1 + 3 \cdot 2^0 = 37 = 3221 = 3 \cdot 2^3 + 2 \cdot 2^2 + 2 \cdot 2^1 + 1 \cdot 2^0$

We observe that we can calculate the carry from column i, by looking only at columns i - 1 and i - 2.

| carries: | 3 | 2 | 2 | 3 |   |

|----------|---|---|---|---|---|

|          |   | 3 | 2 | 1 | 3 |

| +        |   | 3 | 2 | 1 | 3 |

|          | 3 | 2 | 2 | 1 | 0 |

(日) (同) (日) (日)

Addition in ℕ

A I MA

(日) (同) (日) (日)

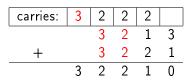

Let us calculate addition of two natural numbers using ambiguous arithmetic notation. That is a representation of natural numbers in binary, except that digits 0, 1, 2, 3 may be used. For example:

$3213 = 3 \cdot 2^3 + 2 \cdot 2^2 + 1 \cdot 2^1 + 3 \cdot 2^0 = 37 = 3221 = 3 \cdot 2^3 + 2 \cdot 2^2 + 2 \cdot 2^1 + 1 \cdot 2^0$

We observe that we can calculate the carry from column i, by looking only at columns i - 1 and i - 2.

| carries: | 3 | 2 | 2 | 3 |   |

|----------|---|---|---|---|---|

|          |   | 3 | 2 | 1 | 3 |

| +        |   | 3 | 2 | 1 | 3 |

|          | 3 | 2 | 2 | 1 | 0 |

Let us calculate addition of two natural numbers using ambiguous arithmetic notation. That is a representation of natural numbers in binary, except that digits 0, 1, 2, 3 may be used. For example:

$3213 = 3 \cdot 2^3 + 2 \cdot 2^2 + 1 \cdot 2^1 + 3 \cdot 2^0 = 37 = 3221 = 3 \cdot 2^3 + 2 \cdot 2^2 + 2 \cdot 2^1 + 1 \cdot 2^0$

We observe that we can calculate the carry from column i, by looking only at columns i - 1 and i - 2.

| carries: | 3 | 2 | 2 | 3 |   |

|----------|---|---|---|---|---|

|          |   | 3 | 2 | 1 | 3 |

| +        |   | 3 | 2 | 1 | 3 |

|          | 3 | 2 | 2 | 1 | 0 |

(日) (同) (日) (日)

Addition in ℕ

A I MA

(日) (同) (日) (日)

Let us calculate addition of two natural numbers using ambiguous arithmetic notation. That is a representation of natural numbers in binary, except that digits 0, 1, 2, 3 may be used. For example:

$3213 = 3 \cdot 2^3 + 2 \cdot 2^2 + 1 \cdot 2^1 + 3 \cdot 2^0 = 37 = 3221 = 3 \cdot 2^3 + 2 \cdot 2^2 + 2 \cdot 2^1 + 1 \cdot 2^0$

We observe that we can calculate the carry from column i, by looking only at columns i - 1 and i - 2.

| carries: | 3 | 2 | 2 | 3 |   |

|----------|---|---|---|---|---|

|          |   | 3 | 2 | 1 | 3 |

| +        |   | 3 | 2 | 1 | 3 |

|          | 3 | 2 | 2 | 1 | 0 |

Let us calculate addition of two natural numbers using ambiguous arithmetic notation. That is a representation of natural numbers in binary, except that digits 0, 1, 2, 3 may be used. For example:

$3213 = 3 \cdot 2^3 + 2 \cdot 2^2 + 1 \cdot 2^1 + 3 \cdot 2^0 = 37 = 3221 = 3 \cdot 2^3 + 2 \cdot 2^2 + 2 \cdot 2^1 + 1 \cdot 2^0$

We observe that we can calculate the carry from column i, by looking only at columns i - 1 and i - 2.

| carries: | 3 | 2 | 2 | 3 |   |

|----------|---|---|---|---|---|

|          |   | 3 | 2 | 1 | 3 |

| +        |   | 3 | 2 | 1 | 3 |

|          | 3 | 2 | 2 | 1 | 0 |

(日) (同) (日) (日)

Let us calculate addition of two natural numbers using ambiguous arithmetic notation. That is a representation of natural numbers in binary, except that digits 0, 1, 2, 3 may be used. For example:

$3213 = 3 \cdot 2^3 + 2 \cdot 2^2 + 1 \cdot 2^1 + 3 \cdot 2^0 = 37 = 3221 = 3 \cdot 2^3 + 2 \cdot 2^2 + 2 \cdot 2^1 + 1 \cdot 2^0$

We observe that we can calculate the carry from column i, by looking only at columns i - 1 and i - 2.

| carries: | 3 | 2 | 2 | 3 |   |

|----------|---|---|---|---|---|

|          |   | 3 | 2 | 1 | 3 |

| +        |   | 3 | 2 | 1 | 3 |

|          | 3 | 2 | 2 | 1 | 0 |

(日) (同) (日) (日)

A I MA

(日) (同) (日) (日)

Let us calculate addition of two natural numbers using ambiguous arithmetic notation. That is a representation of natural numbers in binary, except that digits 0, 1, 2, 3 may be used. For example:

$3213 = 3 \cdot 2^3 + 2 \cdot 2^2 + 1 \cdot 2^1 + 3 \cdot 2^0 = 37 = 3221 = 3 \cdot 2^3 + 2 \cdot 2^2 + 2 \cdot 2^1 + 1 \cdot 2^0$

We observe that we can calculate the carry from column i, by looking only at columns i - 1 and i - 2.

| carries: | 3 | 2 | 2 | 3 |   |

|----------|---|---|---|---|---|

|          |   | 3 | 2 | 1 | 3 |

| +        |   | 3 | 2 | 1 | 3 |

|          | 3 | 2 | 2 | 1 | 0 |

Addition in ℕ

A I MA

(日) (同) (日) (日)

Let us calculate addition of two natural numbers using ambiguous arithmetic notation. That is a representation of natural numbers in binary, except that digits 0, 1, 2, 3 may be used. For example:

$3213 = 3 \cdot 2^3 + 2 \cdot 2^2 + 1 \cdot 2^1 + 3 \cdot 2^0 = 37 = 3221 = 3 \cdot 2^3 + 2 \cdot 2^2 + 2 \cdot 2^1 + 1 \cdot 2^0$

We observe that we can calculate the carry from column i, by looking only at columns i - 1 and i - 2.

| carries: | 3 | 2 | 2 | 3 |   |

|----------|---|---|---|---|---|

|          |   | 3 | 2 | 1 | 3 |

| +        |   | 3 | 2 | 1 | 3 |

|          | 3 | 2 | 2 | 1 | 0 |

A I MA

(日) (同) (日) (日)

Let us calculate addition of two natural numbers using ambiguous arithmetic notation. That is a representation of natural numbers in binary, except that digits 0, 1, 2, 3 may be used. For example:

$3213 = 3 \cdot 2^3 + 2 \cdot 2^2 + 1 \cdot 2^1 + 3 \cdot 2^0 = 37 = 3221 = 3 \cdot 2^3 + 2 \cdot 2^2 + 2 \cdot 2^1 + 1 \cdot 2^0$

We observe that we can calculate the carry from column i, by looking only at columns i - 1 and i - 2.

| carries: | 3 | 2 | 2 | 3 |   |

|----------|---|---|---|---|---|

|          |   | 3 | 2 | 1 | 3 |

| +        |   | 3 | 2 | 1 | 3 |

|          | 3 | 2 | 2 | 1 | 0 |

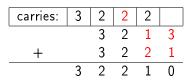

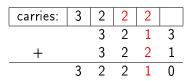

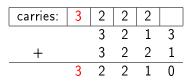

Addition in  $\mathbb{N}$

Similarly:

| carries: | 3 | 2 | 2 | 2 |   |

|----------|---|---|---|---|---|

|          |   | 3 | 2 | 1 | 3 |

| +        |   | 3 | 2 | 2 | 1 |

|          | 3 | 2 | 2 | 1 | 0 |

Thus adding two *n* bit numbers in ambiguous notation can be done via an  $NC^0$  circuit.

Similarly:

Thus adding two *n* bit numbers in ambiguous notation can be done via an  $NC^0$  circuit.

Similarly:

Thus adding two *n* bit numbers in ambiguous notation can be done via an  $NC^0$  circuit.

Similarly:

Thus adding two *n* bit numbers in ambiguous notation can be done via an  $NC^0$  circuit.

Similarly:

Thus adding two *n* bit numbers in ambiguous notation can be done via an  $NC^0$  circuit.

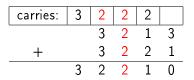

Addition in  $\mathbb{N}$

Similarly:

| carries: | 3 | 2 | 2 | 2 |   |

|----------|---|---|---|---|---|

|          |   | 3 | 2 | 1 | 3 |

| +        |   | 3 | 2 | 2 | 1 |

| -        | 3 | 2 | 2 | 1 | 0 |

Thus adding two *n* bit numbers in ambiguous notation can be done via an  $NC^0$  circuit.

Similarly:

Thus adding two *n* bit numbers in ambiguous notation can be done via an  $NC^0$  circuit.

Similarly:

Thus adding two *n* bit numbers in ambiguous notation can be done via an  $NC^0$  circuit.

Similarly:

Thus adding two *n* bit numbers in ambiguous notation can be done via an  $NC^0$  circuit.

Similarly:

Thus adding two *n* bit numbers in ambiguous notation can be done via an  $NC^0$  circuit.

# 1 Parallelism

- Motivation

- Random Access Machine

- CRAM[t(n)] = IND[t(n)] = FO[t(n)]

# 2 Circuit Complexity

- Basic Definitions

- Addition in  $\mathbb{N}$

- Basic Theorems

A.L.MA.

Thomas Pipilikas Parallelism and Circuit Complexity Parallelism

#### Basic Theorems

## Theorem

# $\mathrm{NC}^i \subseteq \mathrm{AC}^i \subseteq \mathrm{ThC}^i \subseteq \mathrm{NC}^{i+1}$

A.L.MA.

Thomas Pipilikas Parallelism and Circuit Complexity

#### Basic Theorems

## Theorem

For all  $i \in \mathbb{N}$ ,

$NC^{i} \subset AC^{i} \subset ThC^{i} \subset NC^{i+1}$

In order to prove the theorem above we will use the next proposition:

# Proposition

The boolean majority query MAJ is in  $NC^1$ , where

$MAJ \doteq \{\mathcal{A} \in STRUC[\tau_s] \mid \mathcal{A} \text{ contains more than } \|\mathcal{A}\| / 2 \ "1"s\}$

Thomas Pipilikas Parallelism and Circuit Complexity

イロト イロト イミト イミト

#### Basic Theorems

### Theorem

For all  $i \in \mathbb{N}$ ,

$NC^{i} \subset AC^{i} \subset ThC^{i} \subset NC^{i+1}$

In order to prove the theorem above we will use the next proposition:

# Proposition

The boolean majority query MAJ is in  $NC^1$ , where

$MAJ \doteq \{\mathcal{A} \in STRUC[\tau_s] \mid \mathcal{A} \text{ contains more than } \|\mathcal{A}\| / 2 \ "1"s\}$

**Hint:** Build an  $NC^1$  circuit for majority by adding the n input bits via a full binary tree of height log n, by using the ambiguous notation.

We give a sketching of the proof:

## Proof.

The first two containments are obvious (why?).

A.L.MA.

Thomas Pipilikas Parallelism and Circuit Complexity

We give a sketching of the proof:

## Proof.

The first two containments are obvious (why?).

For the third we can simulate any ThC-gate using a circuit of depth log n recognising MAJ. Let threshold gate with threshold value k.

• If  $k \leq ||w|| / 2$  we are just checking if  $w 1^{||w|| - 2k} \in MAJ$ .

(日) (四) (문) (문)

We give a sketching of the proof:

## Proof.

The first two containments are obvious (why?).

For the third we can simulate any ThC-gate using a circuit of depth log n recognising MAJ. Let threshold gate with threshold value k.

- If  $k \leq ||w|| / 2$  we are just checking if  $w 1^{||w|| 2k} \in MAJ$ .

- If k > ||w|| / 2, we are just checking if  $w0^{2k ||w||} \in MAJ$ .

・ロト ・同ト ・ヨト ・ヨト

We give a sketching of the proof:

## Proof.

The first two containments are obvious (why?).

For the third we can simulate any ThC-gate using a circuit of depth log n recognising MAJ. Let threshold gate with threshold value k.

- If  $k \leq ||w|| / 2$  we are just checking if  $w 1^{||w|| 2k} \in MAJ$ .

- If k > ||w|| / 2, we are just checking if  $w0^{2k ||w||} \in MAJ$ .

## Corollary

$$\mathrm{NC} = \mathrm{AC} \doteqdot \bigcup_{\mathbb{N}} \mathrm{AC}^{i} = \mathrm{ThC} \doteqdot \bigcup_{\mathbb{N}} \mathrm{ThC}^{i}$$

Thomas Pipilikas

#### Theorem

For all polynomially bounded and first-order constructible t(n), the following classes are equal:

$$\operatorname{CRAM}[t(n)] = \operatorname{IND}[t(n)] = \operatorname{FO}[t(n)] = \operatorname{AC}[t(n)]$$

Thomas Pipilikas Parallelism and Circuit Complexity

<ロ> (日) (日) (日) (日) (日)

#### Theorem

For all polynomially bounded and first-order constructible t(n), the following classes are equal:

$$\operatorname{CRAM}[t(n)] = \operatorname{IND}[t(n)] = \operatorname{FO}[t(n)] = \operatorname{AC}[t(n)]$$

## Proof.

The equality of the first three classes has been proved.

$\mathfrak{k} \operatorname{FO}[t(n)] \subseteq \operatorname{AC}[t(n)]$

Let  $S \subseteq \text{STRUC}[\tau]$  a FO[t(n)] boolean query given by the quantifier block,  $\text{QB} = (Q_1 x_1 . M_1) ... (Q_k x_k . M_k)$ , initial formula,  $M_0$ , and tuple of constants,  $\overline{c}$ .

#### Proof.

We must write a first-order query, I, to generate circuit  $C_n = I(0^n)$ , so that for all  $\mathcal{A} \in \text{STRUC}[\tau]$ ,

$$\mathcal{A} \models [\mathrm{QB}]^{t(\|\mathcal{A}\|)} \mathit{M}_0\left(\overrightarrow{c}/\overrightarrow{x}

ight) \iff \mathit{C}_{\|\mathcal{A}\|}$$

accepts  $\mathcal{A}$

We must write a first-order query, I, to generate circuit  $C_n = I(0^n)$ , so that for all  $\mathcal{A} \in \text{STRUC}[\tau]$ ,

$$\mathcal{A} \models [\mathrm{QB}]^{t(\|\mathcal{A}\|)} \mathit{M}_{0}\left(\overrightarrow{c}/\overrightarrow{x}

ight) \iff \mathit{C}_{\|\mathcal{A}\|}$$

accepts  $\mathcal{A}$

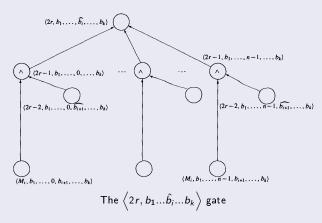

Initially the circuit evaluates the quantifier-free formulas  $M_i$ , where  $i \in n + 1$ . The nodes  $\langle M_i, b_1, ..., b_k \rangle$  will be the gates that have evaluated these formulas, i.e.,

$$\langle M_i, b_1, ..., b_k \rangle (\operatorname{bin} (\mathcal{A})) = 1 \iff \mathcal{A} \models M_i (b_1, ..., b_k)$$

##

#### Basic Theorems

### Proof.

Let  $\varphi^r$  defined as in the proof of  $FO[t(n)] \subseteq CRAM[t(n)]$ . We construct inductively the gate  $\langle 2r, b_1...\hat{b}_i...b_k \rangle$  so that

$$\left\langle 2r,b_{1}...\hat{b_{i}}...b_{k}

ight

angle \left( \mathrm{bin}\left(\mathcal{A}

ight)

ight) =1\iff\mathcal{A}\modelsarphi^{r}\left( b_{1},...,b_{k}

ight)$$

#### Proof.

Let  $\varphi^r$  defined as in the proof of  $\operatorname{FO}[t(n)] \subseteq \operatorname{CRAM}[t(n)]$ . We construct inductively the gate  $\left\langle 2r, b_1...\hat{b}_i...b_k \right\rangle$  so that

$$\left\langle 2r,b_{1}...\hat{b}_{i}...b_{k}

ight

angle ( ext{bin}\left(\mathcal{A}

ight))=1\iff\mathcal{A}\modelsarphi^{r}\left(b_{1},...,b_{k}

ight)$$

This is achieved by letting gate  $\langle 2r, b_1...\hat{b}_i...b_k \rangle$ :

Be "and"-gate ("or"), if  $Q_i = \forall (\exists)$ Has inputs  $\langle 2r - 1, b_1, ..., b_i, \widehat{b_{i+1}}, ..., b_k \rangle$ , where  $b_i \in |\mathcal{A}|$   $\langle 2r - 1, b_1, ..., b_i, \widehat{b_{i+1}}, ..., b_k \rangle$  is a binary "and"-gate whoses inputs are  $\langle M_i, b_1, ..., b_k \rangle$  and  $\langle 2r - 2, b_1, ..., b_i, \widehat{b_{i+1}}, ..., b_k \rangle$

#### Basic Theorems

## Proof.

This circuit can be constructed via a first-order query *I*.

Thomas Pipilikas

Parallelism and Circuit Complexity

A.L.MA.

#### Basic Theorems

## Proof.

$\mathfrak{l} \operatorname{AC}[t(n)] \subseteq \operatorname{IND}[t(n)]$

Let  $I : \text{STRUC}[\tau_s] \to \text{STRUC}[\tau_c]$ , a first-order query and  $C = \{C_i\}_{\mathbb{N} \ge 1} = \{I(0^i)\}_{\mathbb{N} \ge 1}$ , a uniform sequence of AC[t(n)] circuits.

#### Basic Theorems

## Circuit Complexity

## Proof.

$\mathfrak{l} \operatorname{AC}[t(n)] \subseteq \operatorname{IND}[t(n)]$

Let  $I : \text{STRUC}[\tau_s] \to \text{STRUC}[\tau_c]$ , a first-order query and  $C = \{C_i\}_{\mathbb{N} \ge 1} = \{I(0^i)\}_{\mathbb{N} \ge 1}$ , a uniform sequence of AC[t(n)] circuits.

We must wright an inductive formula: